WARNING - CL169 :"ufmtest.sv":40:1:40:6|Pruning unused register wr_data. Make sure that there are no unused intermediate registers. WARNING - CL169 :"ufmtest.sv":40:1:40:6|Pruning unused register wr_rq.

WARNING - CL169 :"ufmtest.sv":40:1:40:6|Pruning unused register rd_rq.

Either assign a value or remove the declaration. WARNING - CG133 :"ufmtest.sv":6:10:6:16|Object counter is declared but not assigned. WARNING - CG133 :"ufmtest.sv":3:11:3:13|Object led is declared but not assigned. If this is not the intended behavior, drive the inputs with valid values, or inputs from the top level.

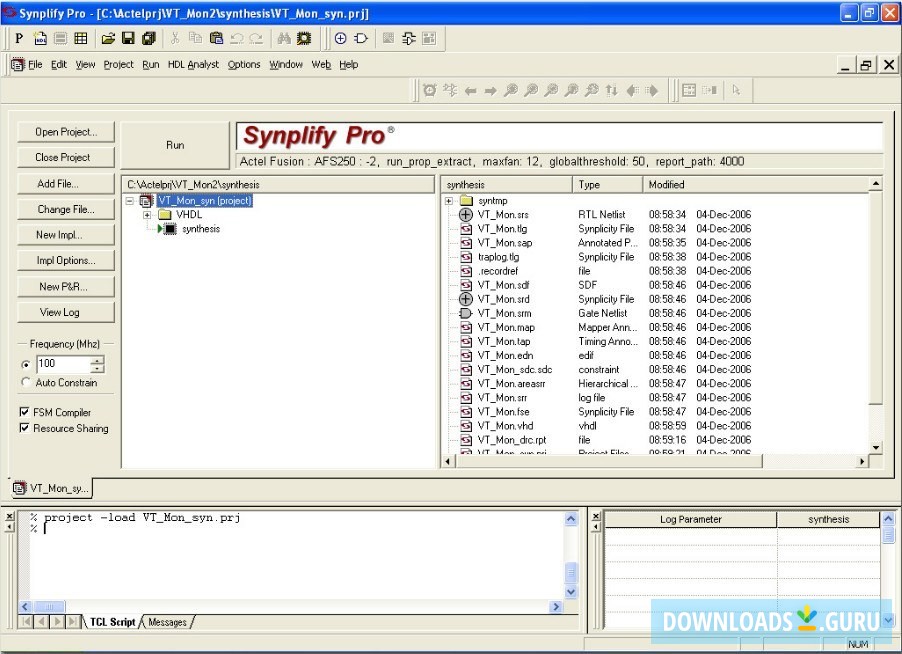

#Synplify pro for win 8 code#

The code of the top level module is as follows: I've just created a very basic test design and it did infer clk as a clock input in Spreadsheet automatically. And it is giving me this warning "WARNING - logical net 'clk' has no load." I've tried adding the same SDC file in Diamond under Synthesis Constraint Files but the synthesizing give me the following error: ERROR - 'clk' matches no clock ports in the design It looks like the design is synthesizable (at least I don't see any warnings that it isn't) Edit: must me something with this particular design, not synthesizable somehow after all. I open Synpify Pro (from the Diamond toolbar) add an SDC file (under Logic Constraints) and add a clock there as follows (done in trough the SCOPE ui on the clocks tab): define_clock -freq 50 -clockgroup default_clkgroup_0 But back in Diamond I re-synthesize the design and the clk input is still appearing under "unconnected" in Spreadsheet View. Synpify Pro does say that clk is an inferred clock and I need to add a constraint for it.

#Synplify pro for win 8 how to#

I have a clk input in my top-level module but cannot figure out how to make it appear as a clock input under Spreadsheet View. With Verilog files it allows to use the built-in Lattice LSE synthesizer but with SV files it requires to use Synpify Pro. Lattice Diamond 64bit 3.8.0.115.3 (Windows 7) Trying synthesize a simple project with 3 System Verilog files.

0 kommentar(er)

0 kommentar(er)